# Take the Leap: From MCUs to FPGAs

Spend a year with me as I use my MCU and software background as a base from which to explore the strange land of programmable logic

#### Positive Edge LLC<sup>®</sup> Field Programmable Gate Array –

# **P**rogrammable Gate

**A**rrays

#### Key Take Aways

- Why you might want to use an FPGA

- Exposure to some of the most common traps that trip up FPGA beginners

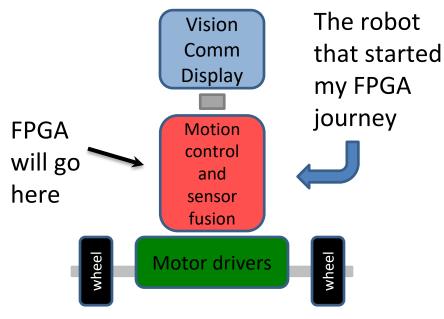

### Where I came from

- First soldering iron burn on finger: 1975

- Digital electronics 30 years ago

- Software off and on for a long time

- MCUs for a decade +

- Picked up robots in the 21<sup>st</sup> century because they're modern

### My Role in All of This

- Ever asked a question where the answer was a smug "RTFM"?

- I spent a year asking those dumb questions so, in theory, you won't have to. You're welcome to anyway, but it won't be mandatory.

Bad clip-art that came with this presentation software representing me

### Take the Leap: from MCUs to FPGAs. But watch out for alligators

**Duane Benson**

| 1  | library ieee;                                                |  |  |  |  |  |  |  |

|----|--------------------------------------------------------------|--|--|--|--|--|--|--|

| 2  | <pre>use ieee.std_logic_1164.all;</pre>                      |  |  |  |  |  |  |  |

| 3  | <pre>use ieee.std_logic_unsigned.all;</pre>                  |  |  |  |  |  |  |  |

| 4  | Library UNISIM;                                              |  |  |  |  |  |  |  |

| 5  | use UNISIM.vcomponents.all;                                  |  |  |  |  |  |  |  |

| 6  |                                                              |  |  |  |  |  |  |  |

| 7  | entity ledflash is                                           |  |  |  |  |  |  |  |

| 8  | Port ( CLK_66MHZ : in STD_LOGIC;                             |  |  |  |  |  |  |  |

| 9  | USER_RESET : in STD_LOGIC;                                   |  |  |  |  |  |  |  |

| 10 | LED : out STD_LOGIC_VECTOR (3 downto 0));                    |  |  |  |  |  |  |  |

| 11 | end ledflash;                                                |  |  |  |  |  |  |  |

| 12 |                                                              |  |  |  |  |  |  |  |

| 13 | architecture Behavioral of ledflash is                       |  |  |  |  |  |  |  |

| 14 | <pre>signal clk : std_logic;</pre>                           |  |  |  |  |  |  |  |

| 15 | <pre>signal clk_enable : std_logic;</pre>                    |  |  |  |  |  |  |  |

| 16 | <pre>signal led_count : std_logic_vector(26 downto 0);</pre> |  |  |  |  |  |  |  |

| 17 | Pbegin                                                       |  |  |  |  |  |  |  |

| 18 | <pre>clk_enable &lt;= not USER_RESET;</pre>                  |  |  |  |  |  |  |  |

| 19 | BUFGCE_inst : BUFGCE                                         |  |  |  |  |  |  |  |

| 20 | port map (                                                   |  |  |  |  |  |  |  |

| 21 | 0 => clk,                                                    |  |  |  |  |  |  |  |

| 22 | CE => clk_enable,                                            |  |  |  |  |  |  |  |

| 23 | I => CLK_66MHZ                                               |  |  |  |  |  |  |  |

| 24 | );                                                           |  |  |  |  |  |  |  |

| 25 |                                                              |  |  |  |  |  |  |  |

| 26 | process (clk)                                                |  |  |  |  |  |  |  |

| 27 | begin                                                        |  |  |  |  |  |  |  |

| 28 | if clk='1' and clk'event then                                |  |  |  |  |  |  |  |

| 29 | <pre>led_count &lt;= led_count + 1;</pre>                    |  |  |  |  |  |  |  |

| 30 | end if;                                                      |  |  |  |  |  |  |  |

| 31 | end process;                                                 |  |  |  |  |  |  |  |

| 32 | LED <= led_count(26 downto 23);                              |  |  |  |  |  |  |  |

| 33 | end Behavioral;                                              |  |  |  |  |  |  |  |

Image from tinyFPGA.com

## Why FPGAs?

- Extreme customization

- Parallel work

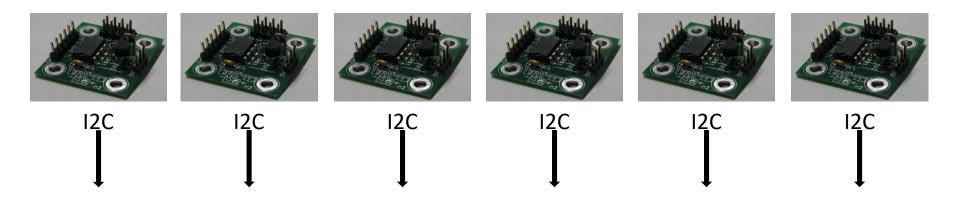

### Why FPGAs?

• And this: Parallel work

#### All loaded into the FPGA and processed at the same time.

#### **FPGAs:**

- Not as big a jump as I had thought

- Not as expensive as I had thought

- There are quite a number of inexpensive and (relatively) easy to use tools available

But – There are a few dangerous traps – especially if you come with an MCU mindset

#### What's the Same vs. Not the Same

- Use an IDE

- Multiple files in the development set

- Multiple language options

- You code, then implement

- Often familiar syntax

- No instant start at power-up

- The FPGA isn't "running" your code\*

- You are designing a piece of hardware

- You must wire up the chip pins to the innards

- Most pins are not-mapped to a function

## Time to Dig In

- What do you need?

- Digital logic knowledge

- Programming experience will both help and hurt

- Familiarity with IDEs

- MCU programming experience may be more relevant than OS or applications programming

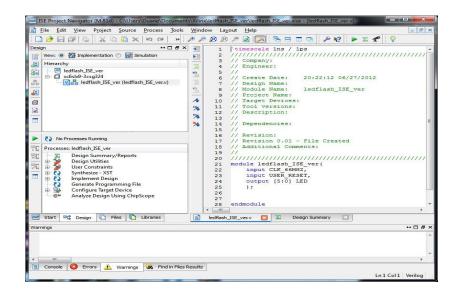

#### **Development environment**

• Lattice, Xilinx, Altera/Intel all have their own IDEs

• That's nice of them

Open source toolchains are around now too

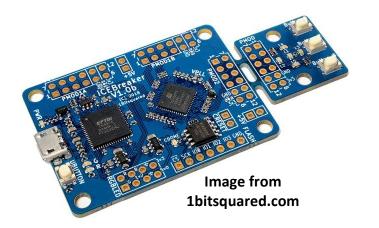

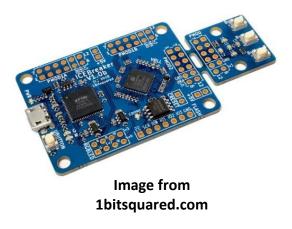

### Pick Your Board

• Now What?

- ngs?

- How do you "program" these things?

- Some will say: "Technically, it's not a program." But what is it? How do you make an FPGA do something?

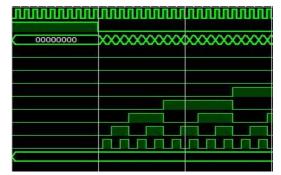

| Bus/Signal       | x         | 0      | 0      | 640      | 1280 | 1920 | 2560 | 3200 | 3840 |    |   | 6400 |   |  | 10240 |    |   |     |    |

|------------------|-----------|--------|--------|----------|------|------|------|------|------|----|---|------|---|--|-------|----|---|-----|----|

| /spi_clk         | 1         | 1      |        |          |      |      |      |      |      |    |   |      |   |  |       |    |   |     |    |

| -/SCLKio_OBUF    | 0         | 0      |        |          |      |      |      |      | Ľ    |    | 1 |      | 1 |  |       |    |   |     |    |

| -/MOSI           | o         | 0      |        |          |      |      |      |      |      |    |   |      |   |  |       |    |   |     |    |

| /LED2_OBUF       | 1         | 1      |        |          |      |      |      |      | 1    |    |   |      |   |  |       |    |   |     |    |

| /SS              | 1         | 1      |        |          |      |      |      |      |      |    |   |      |   |  |       |    |   |     |    |

| •                | • • •     |        |        |          |      |      |      |      |      | 11 |   |      |   |  |       |    |   |     |    |

| Waveform capture | ed Dec 11 | 1, 201 | 2 12:2 | 29:05 AM |      |      |      |      |      |    |   |      |   |  |       | x: | 0 | • • | 0: |

### Order of Work

1. Define "constraints" in UCF/LPF

- 2. Code in your HDL

- 3. Simulate

#### 4. Synthesize

# 5. Crunch to bit file6. Load bit file to device

Empty hardware

Configured and working thing

#### Three primary file Types

Defines pins, port names and locations Core of your HDL code

Library/Code module snippets (includes)

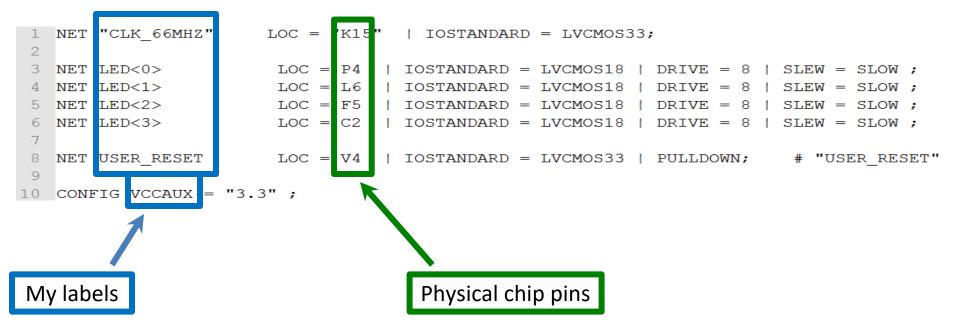

# UCF/LPF: Mapping/defining pins

| 1  | NET "CLK_66MHZ"     | LOC = "K15"   IOSTANDARD = LVCMOS33;                         |

|----|---------------------|--------------------------------------------------------------|

| 2  |                     |                                                              |

| 3  | NET LED<0>          | LOC = P4   IOSTANDARD = LVCMOS18   DRIVE = 8   SLEW = SLOW ; |

| 4  | NET LED<1>          | LOC = L6   IOSTANDARD = LVCMOS18   DRIVE = 8   SLEW = SLOW ; |

| 5  | NET LED<2>          | LOC = F5   IOSTANDARD = LVCMOS18   DRIVE = 8   SLEW = SLOW ; |

| 6  | NET LED<3>          | LOC = C2   IOSTANDARD = LVCMOS18   DRIVE = 8   SLEW = SLOW ; |

| 7  |                     |                                                              |

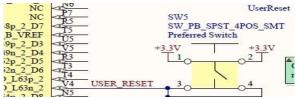

| 8  | NET USER_RESET      | LOC = V4   IOSTANDARD = LVCMOS33   PULLDOWN; # "USER_RESET"  |

| 9  |                     |                                                              |

| 10 | CONFIG VCCAUX = "3. | 3";                                                          |

#### User Constraints File / logical Preferences File, or equivalent

### Anatomy Of The UCF/LPF

User Constraints File / logical Preferences File, or equivalent

# UCF/LPF: Mapping/defining pins

User Constraints File / logical Preferences File, or equivalent

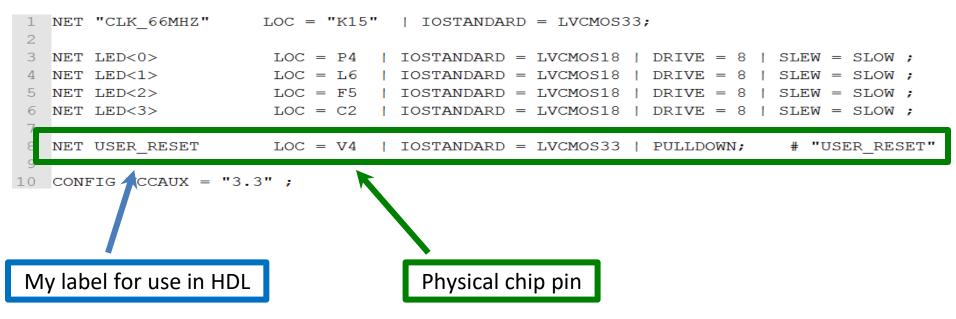

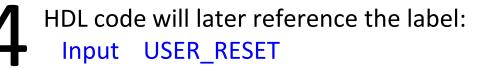

#### First – Define Connections

NET USER\_RESET LOC = V4 | IOSTANDARD = LVCMOS33 | PULLDOWN; # "USER\_RESET"

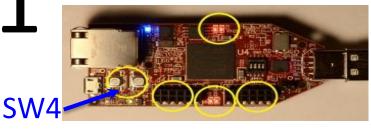

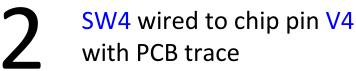

Switch on PCB: SW4

Write UCF to map chip pins to labels: NET USER\_RESET LOC = V4

Positive Edge LLC<sup>®</sup>

"NET" and "LOC" are reserved words, "V4" is the chip pin, "USER\_RESET" is my label

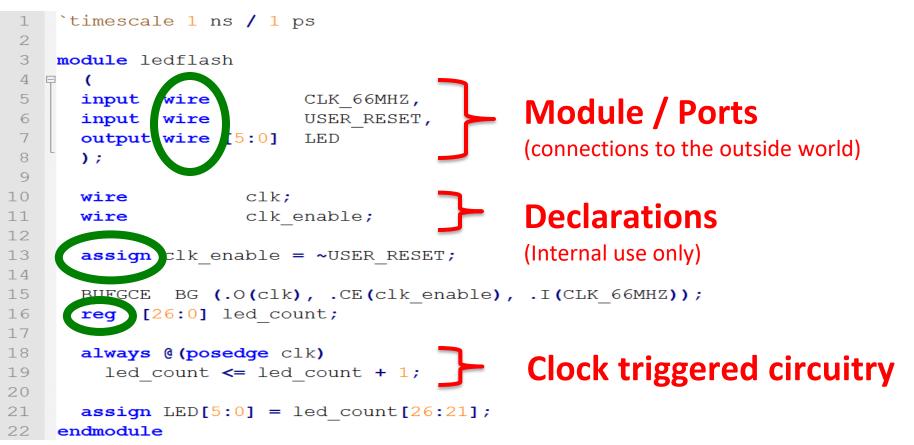

#### Anatomy Of a Verilog File

```

`timescale 1 ns / 1 ps

2

3

module ledflash

4

CLK 66MHZ,

5

input wire

Module / Ports

input wire

USER RESET,

6

7

output wire [5:0]

LED

(connections to the outside world)

8

);

9

clk;

10

wire

Declarations

11

wire

clk enable;

12

(Internal use only)

13

assign clk enable = ~USER RESET;

14

15

BUFGCE BG (.O(clk), .CE(clk enable), .I(CLK 66MHZ));

16

reg [26:0] led count;

17

18

always @ (posedge clk)

Clock triggered circuitry

led_count <= led_count + 1;</pre>

19

20

21

assign LED[5:0] = led count[26:21];

22

endmodule

```

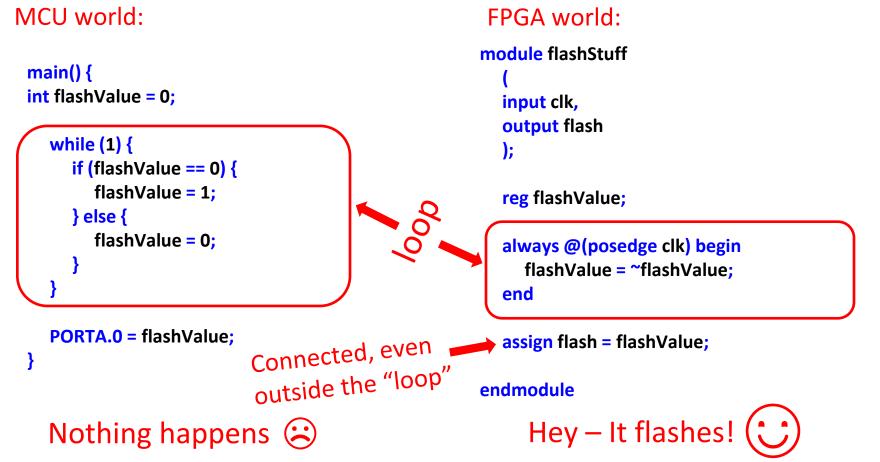

## Wire / Register / Assign

## Wire / Register / Assign

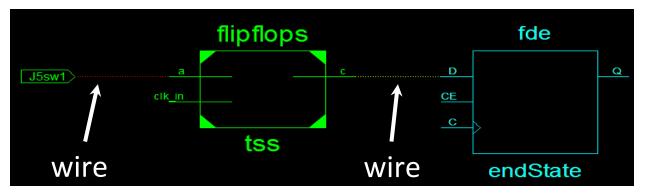

Blinding flash of the obvious here: Wires just go between two things. Obvious, yes. But it needs to be stated in the "new to FPGA" world.

It's not a register like a hardware register in your MCU. It stores value or state logically to combine with another register value – more like a RAM location or variable, although some people don't like that comparison.

"Assign" creates a permanent connection

## Wire / Register / Assign

#### A few important rules

assign awire = aregister\_or\_awire

Only a "wire" can be on the left of the = sign in an assign statement.

An assign cannot be used within an always block "assign" means to wire something up at configuration time.

```

always @(posedge clk) beginareg = aregorareg = aregorareg = awireorareg = awireorareg = awireorareg = awirewhen inside of an always block

```

Both wires and registers can be on the right side anywhere

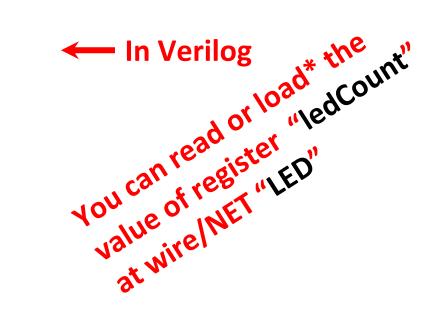

# It's not an array, it's a ribbon cable – sort of

NET LED<0>LOC = P4 | IOSTANDARD = LVCMOS18 | DRIVE = 8 | SLEW = SLOW ;NET LED<1>LOC = L6 | IOSTANDARD = LVCMOS18 | DRIVE = 8 | SLEW = SLOW ;NET LED<2>LOC = F5 | IOSTANDARD = LVCMOS18 | DRIVE = 8 | SLEW = SLOW ;NET LED<3>LOC = C2 | IOSTANDARD = LVCMOS18 | DRIVE = 8 | SLEW = SLOW ;

#### output wire [5:0] LED ... reg [15:0] ledCount = 16'hFFFF;

```

always @(posedge clk) begin

ledCount <= ledCount + 1;

End

```

assign LED[3:0] = ledCount [15:12];

#### Two-types of Logic in your FPGA

Clocked (triggered) vs. Combinatorial (AKA combinational)

### **Clocked logic: Always block**

```

`timescale 1 ns / 1 ps

2

3

module ledflash

Ę

4

(

input wire CLK 66MHZ,

5

input wire USER_RESET,

6

7

output wire [5:0] LED

8

);

9

clk;

10

wire

11

wire

clk enable;

12

13

assign clk enable = ~USER RESET;

14

15

BUFGCE BG (.O(clk), .CE(clk enable), .I(CLK 66MHZ));

16

reg [26:0] led count;

17

18

always @ (posedge clk)

Clock triggered circuitry

led_count <= led_count + 1;</pre>

19

20

21

assign LED[5:0] = led count[26:21];

22

endmodule

```

#### Parallel Activity with Always Blocks

#### Common clock

```

always @(posedge clk_1) begin

flashValueR = ~flashValueR;

end

```

```

always @(posedge clk_1) begin

flashValueG = ~flashValueG;

end

```

```

always @(posedge clk_1) begin

flashValueB = ~flashValueB;

end

```

#### Independent clocks

```

always @(posedge clk_1) begin

flashValueR = ~flashValueR;

end

```

always @(posedge clk\_2) begin flashValueG = ~flashValueG; end

always @(posedge clk\_3) begin

flashValueB = ~flashValueB;

end

You can have many on the same clock or on different\* clocks

#### Combanatorial Logic: assign statement

Positive Edge LLC<sup>®</sup>

```

assign clk_enable = ~USER_RESET;

BUFGCE BG (.0(clk), .CE(clk_enable), .I(CLK_66MHZ));

reg [26:0] led_count;

always @(posedge clk)

led_count <= led_count + 1;

assign LED[5:0] = led count[26:21];

assign GATE_OUT_Y = GATE_IN_A & GATE_IN_B;

endmodule

```

Connected, even outside the "loop" Results happen instantly (less propagation delay) without need for a clock

#### Combinatorial: Connected at start

Positive Edge LLC<sup>®</sup>

# MCU vs. FPGA: Parallel vs. serial

module flashStuff

- some Verilog stuff

always @(posedge clk) begin Some stuff 1; end

always @(posedge clk) begin Some stuff 2; end

always @(posedge clk) begin Some stuff 3;

#### end

- some Verilog stuff endmodule FPGA world: Simultaneously

main() {

- some C code

funct\_1(); funct\_2(); funct\_3(); Func\_

n sequence

- some C code

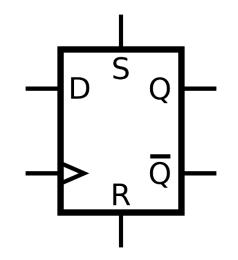

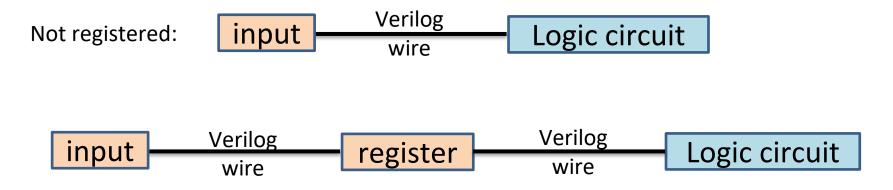

### "Registering"

Experts talked about "registering" a signal

Brain thinks:

"Registering"... Maybe like registering a Windows .dll or something...

Major case of overthinking. "Registering" just means put the signal in a register

## Blocking / Non-blocking

- = **blocking** (better described as "immediate" real time game)

- <= non-blocking (clock based like a turn based game. You do stuff and read it all at the end of the turn)

assign GATE\_OUT\_Y = GATE\_IN\_A & GATE\_IN\_B;

Blocking: "GATE\_OUT\_Y" will always, immediately reflect the reults of "GATE\_OUT\_A" AND "GATE\_OUT\_B"

```

always @(posedge clk)

led_count <= led_count + 1;</pre>

```

Non-blocking: "led\_count" will only be accurate after clock cycle

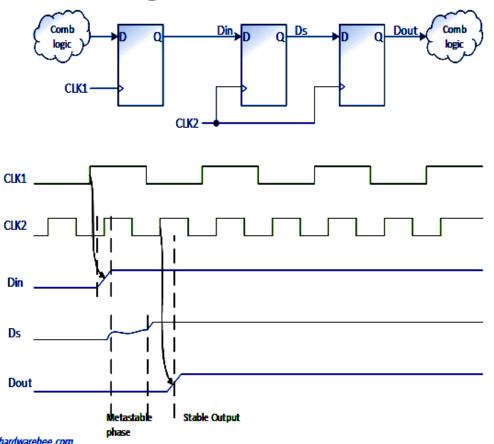

## Metastability - Warning

- Clock sampling too soon

- Transition from 0 to 1 or 1 to 0 not complete yet

- Results in an unknown output

- Often caused by asynchronous inputs or using multiple clock domains

### Metastability - Warning

- From the MCU world, think about key bounce, but worse and easier to solve (not an exact analogy, but close enough)

- Better to use once clock source

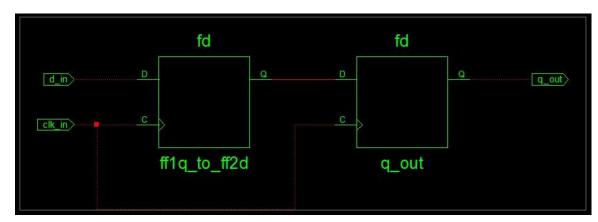

- Mitigated by using two or three flip flops in series

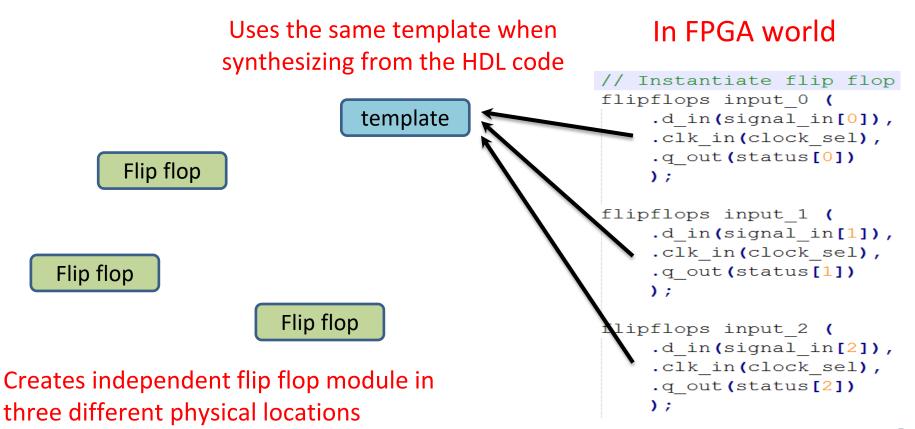

# Anatomy of Libraries & Modules

- VHDL has standard and user developed libraries

- Verilog code can be separated out as a module

They look like typical software libraries and functions

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.all;

```

```

Library UNISIM;

use UNISIM.vcomponents.all;

```

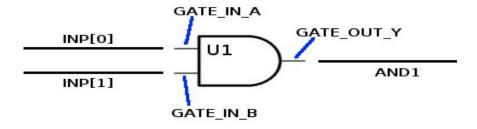

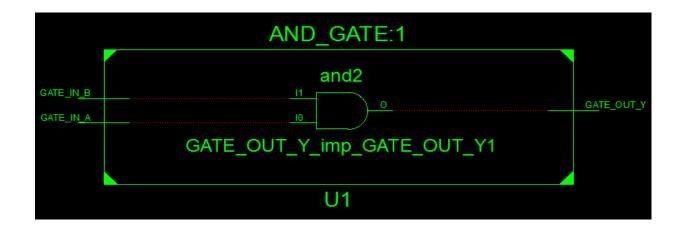

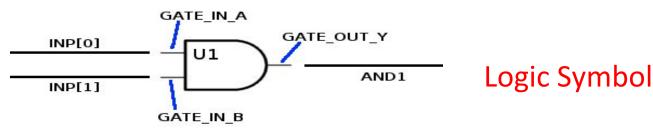

#### Simple Example

#### Simple Example

#### The module In Verilog:

```

imodule AND_GATE(

input GATE_IN_A,

input GATE_IN_B,

output GATE_OUT_Y

);

assign GATE_OUT_Y = GATE_IN_A & GATE_IN_B;

endmodule

```

Used in another Verilog file Rather than "call", the term "Instantiate" is used.

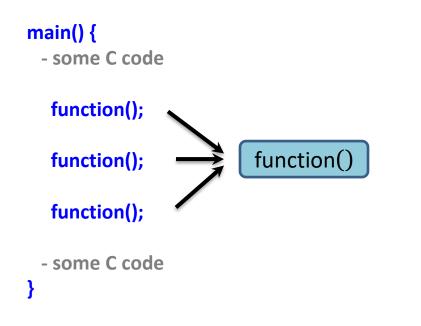

# Not the Same as Calling a Function

In the MCU software world

Calls the same physical code each time (unless multi-threaded, but that's not the analogy)

# Not the Same as Calling a Function

#### Conclusions

- I've only touched the surface

- The barriers to FPGA entry have dropped

- A lot of options

- A lot of opportunities for confusion and MCU-derived traps

- But, they are amazing tools once you get to know them.

Download this presentation at: positiveedge.today/teardown-2023-mcu-to-fpga